Inzicht in de kracht van de S-R Latch: een toegangspoort tot moderne elektronica

Vergrendeling zijn eenvoudige digitale apparaten die een beetje informatie opslaan en die waarde bewaren totdat deze nieuwe invoersignalen krijgt.Ze worden in digitale systemen gebruikt om binaire gegevens tijdelijk te bewaren.Vergrenkingen kunnen worden gemaakt met behulp van verschillende soorten basislogische poorten zoals en, of niet, NAND en NOR -poorten.Dit artikel onderzoekt het ontwerp, de functie, de variaties en het gebruik van de S-R-grendel en benadrukt de beste rol in moderne elektronica en het gebruik ervan in praktische circuits en digitale logica-simulaties.Catalogus

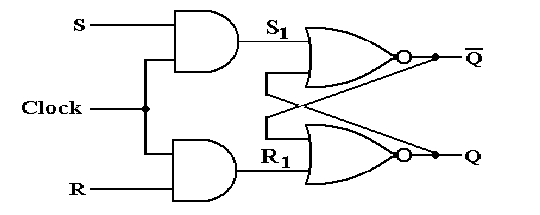

Figuur 1: S-R Latch Circuit Diagram

Structuur van de S-R-gloe

De S-R (Set-Reset) Latch, een hoeksteen in digitale elektronica, is een bistabiele multivibrator.Het is in staat om een van de twee verschillende, stabiele toestanden voor onbepaalde tijd zonder externe invoer te handhaven.Deze functionaliteit maakt de SR -vergrendeling tot een hoofdcomponent in geheugenopslag- en schakelbewerkingen op verschillende elektronische apparaten.

Structureel bestaat de SR -vergrendeling uit twee onderling verbonden noch poorten gerangschikt in een feedback -lusontwerp.Deze specifieke regeling is belangrijk omdat het de vereisten biedt voor bistabiliteit.De output van elke NOR -poort is rechtstreeks verbonden met de invoer van de andere, waardoor een continue lus van feedback wordt gecreëerd die de werking van de vergrendeling ondersteunt.

Afbeelding 2: S-R Latch en het kloksignaal (CLK)

Uitbreiding van het basisontwerp introduceert de Gated SR -vergrendeling een extra, input: het kloksignaal (CLK).Deze verbetering bevat een klokinvoer die besturingslaag biedt, waardoor de vergrendelingsbewerkingen worden geïntegreerd in systemen die synchronisatie vereisen.Deze synchronisatie verplicht omdat het de precieze momenten bepaalt waarop de vergrendeling van toestand kan veranderen, toepasselijk beschreven door de term 'gated'.De opname van het kloksignaal zorgt ervoor dat wijzigingen in de uitgangsstatus van de vergrendeling alleen optreden tijdens de actieve klokfase, meestal aan de stijgende of dalende rand van het CLK -signaal.

De introductie van de CLK -input behoudt niet alleen de eigenschappen van de basis SR -vergrendeling, maar stemt ook de werking van de tijdelijke dynamiek van grotere digitale systemen in.Deze afstemming wens voor het handhaven van gegevensintegriteit en ervoor zorgen dat de overgangen van de toestand optreden zonder glitches of onbedoelde veranderingen, met name in complexe circuitconfiguraties waar meerdere vergrendelingen kunnen interageren.Door te controleren wanneer de vergrendeling op de set- en resetopdrachten reageert, kan het systeem problemen zoals raceomstandigheden en andere timinggerelateerde fouten vermijden die anders de stabiliteit en prestaties van het systeem kunnen verstoren.

Operationele staten van de S-R Latch

De werking ervan hangt af van de ingangen van twee besturingssignalen: set (s) en reset (r).Hier leggen we uit hoe deze inputs de uitgangen en de toestanden van de SR -vergrendeling beïnvloeden.

Case 1: Stel voorwaarde in

Wanneer de set (s) ingang hoog is (1) en de reset (R) ingang laag is (0), voert de vergrendeling de ingestelde toestand in.In deze toestand zal de NAND-poort die is aangesloten op de R-ingang een laag signaal uitvoert vanwege de hoge ingang van S. Dit lage signaal zorgt ervoor dat de tweede NAND-poort een hoog signaal uitvoert, waardoor Q wordt ingesteld op hoog (1) en Q-barte laag (0).Deze toestand is stabiel en houdt q hoog totdat de ingangen veranderen, waaruit blijkt dat het vermogen van de vergrendeling om een hoge toestand op te slaan.

Afbeelding 3: De ingestelde status

Case 2: Reset Condition

Wanneer S laag is (0) en R hoog is (1), voert de vergrendeling de resetconditie in.Hier maakt de hoge ingang op R en de lage ingang op S de NAND -poort aangesloten op R -uitgang een laag signaal.Dit lage signaal stelt Q in op laag (0) en Q-bar op hoog (1), waardoor de vergrendeling effectief wordt gereset.Dit toont het vermogen van de vergrendeling om terug te keren naar een stabiele lage toestand in Q wanneer de juiste ingangen krijgen.

Figuur 4: De resetstatus

Geval 3: Ongeldige staat

Als zowel S als R laag zijn (0), zijn beide ingangen voor de NAND-poorten laag, waardoor beide uitgangen Q en Q-bar hoog worden.Deze toestand wordt ongeldig of verboden genoemd omdat het de basisregel overtreedt dat Q en Q-bar altijd tegenstellingen moeten zijn.Dit scenario benadrukt de beperking van de SR -vergrendeling en benadrukt het belang van het vermijden van dergelijke onstabiele toestanden door het juiste inputbeheer.

Figuur 5: De ongeldige staat

Case 4: Houd staat voor

Wanneer beide ingangen hoog zijn (1), zijn de uitgangen afhankelijk van de vorige status van de vergrendeling in plaats van de huidige ingangen.Dit staat bekend als de hold-conditie, waarbij Q en Q-Bar ongewijzigd blijven, waardoor de laatste geldige status van de vergrendeling wordt behouden.Voor sommige toepassingen is het belangrijk om de vergrendelde toestand gedurende lange tijd te kunnen handhaven zonder aanpassing, zoals geheugenopslagcellen waar gegevensintegriteit van groot belang is.

Figuur 6: De hold -status

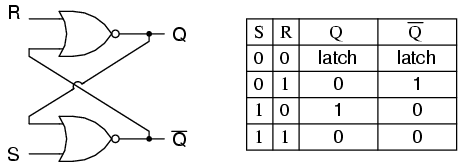

S-R Latch met een waarheidstabel

Deze tabel is niet alleen een theoretisch hulpmiddel, maar het is ook praktisch voor zowel circuitontwerpers als studenten.Het helpt hen te zien hoe de vergrendeling zich onder veel omstandigheden gedraagt.Hieronder presenteren we de uitgebreide waarheidstabel voor de SR -vergrendeling, gevolgd door verklaringen en praktische inzichten voor elke aandoening.

|

S |

R |

Q |

Q-bar |

STAAT |

|

0 |

0 |

1 |

1 |

Ongeldig |

|

0 |

1 |

0 |

1 |

Resetten |

|

1 |

0 |

1 |

0 |

Set |

|

1 |

1 |

Q |

Q-bar |

Uitstel |

Grafiek 1: SR

Latch Truth Table

Verklaring van elke rij

Stel voorwaarde (s = 1, r = 0) in: deze rij laat zien dat wanneer s hoog is en R laag is, Q is ingesteld op hoog (1) en Q-bar op laag (0).Dit weerspiegelt de reactie van het circuit op een set -opdracht, waardoor een '1' effectief wordt opgeslagen.

Reset Condition (S = 0, R = 1): hier geven de ingangen een reset -bewerking aan.Bijgevolg wordt Q gereset op laag (0) en is Q-bar ingesteld op hoog (1).Deze staat toont het vermogen van de vergrendeling om terug te keren naar een '0'.

Ongeldige toestand (s = 0, r = 0): beide uitgangen worden hoog in deze toestand, wat in het algemeen wordt vermeden omdat dit resulteert in beide outputs die identiek zijn.Dit kan leiden tot instabiliteit of niet-gedefinieerd gedrag in de vergrendeling, omdat het de regel schendt dat Q en Q-Bar altijd tegenstellingen moeten zijn.

Houd de staat vast (s = 1, r = 1): in dit scenario behoudt de vergrendeling zijn vorige status, waarmee het vermogen wordt getoond om de laatste set -status vast te houden, tenzij expliciet bevolen te veranderen.

Praktische inzichten en tips

Inzicht in output: onthoud altijd dat Q en Q-Bar idealiter complements zijn.Elke afwijking van deze regel (zoals te zien in de ongeldige toestand) duidt op een probleem of verkeerde configuratie.

Het vermijden van de ongeldige toestand: het is noodzakelijk dat ontwerpers ervoor zorgen dat de situatie waarin S en R beide laag zijn.Het implementeren van extra logica of vergrendeling kan deze status helpen voorkomen.

Gebruikmakend van de voorwaarde: de voorwaarde kan met name handig zijn in applicaties die in de loop van de tijd gegevensbehoud vereisen.Het handhaven van gegevensintegriteit kan afhangen van ervoor te zorgen dat de vergrendeling niet onbedoeld in de set of reset -status gaat.

Door de waarheidstabel te interpreteren: verwijs bij het ontwerpen of debuggen van circuits de waarheidstabel om te voorspellen hoe veranderingen in de input de output zullen beïnvloeden, vooral in complexe circuits waar meerdere vergrendelingen worden gebruikt.

Functionele dynamiek van de S-R Latch

De S-R (Set-Reset) Latch werkt alleen goed als de ingangen correct worden beheerd.Om te begrijpen hoe het functioneert, moet u weten hoe verschillende invoercombinaties de uitgangen, Q en Q-Bar beïnvloeden (het tegenovergestelde van Q).

Figuur 7: S-R Latch

Als zowel set (s) als reset (r) tegelijkertijd worden geactiveerd (s = 1 en r = 1), gaat de vergrendeling in een "verboden toestand", waarbij beide uitgangen, q en q-bar, 0 zijn.Dit is een probleem omdat normaal gesproken q en q-bar tegenstellingen moeten zijn.

Onder normale omstandigheden, om de vergrendeling in te stellen, activeert u S (set S op 1) en deactiveer R (set R op 0).Dit zorgt ervoor dat Q hoog (1) en Q-Bar Low Go Low (0) gaat, waaruit blijkt dat de vergrendeling een 1. kan opslaan. Om de vergrendeling te resetten, activeert u R (set R op 1) en deactiveert S (set S op 0).Hierdoor worden Q laag (0) en Q-bar hoog (1), waaruit blijkt dat de vergrendeling zichzelf kan verwijderen en een 0 kan opslaan.

Wanneer beide ingangen worden gedeactiveerd (s = 0 en r = 0), houdt de vergrendeling zijn laatste status, set of reset.Dit is goed voor het opslaan van gegevens of het bewaren van een staat zonder continue input nodig te hebben.

Race-omstandigheden kunnen de werking van de S-R-Latch bemoeilijkt.Deze fouten vinden plaats wanneer de uitgangen sterk afhankelijk zijn van de timing van invoerwijzigingen, wat leidt tot onvoorspelbare resultaten als de ingangen op bijna dezelfde tijd veranderen.Om dit te voorkomen en ervoor te zorgen dat de vergrendeling betrouwbaar werkt, worden tijdvertragingsmechanismen vaak gebruikt.Deze vertragingen zorgen ervoor dat de ene input wordt geactiveerd nadat de andere tijd heeft gehad om te stabiliseren.Om de vergrendeling te gebruiken in digitale circuits waar precieze timing vereist is, moet deze consistent presteren en gestage uitgangen behouden.Dit wordt mogelijk gemaakt door de gecontroleerde timing.

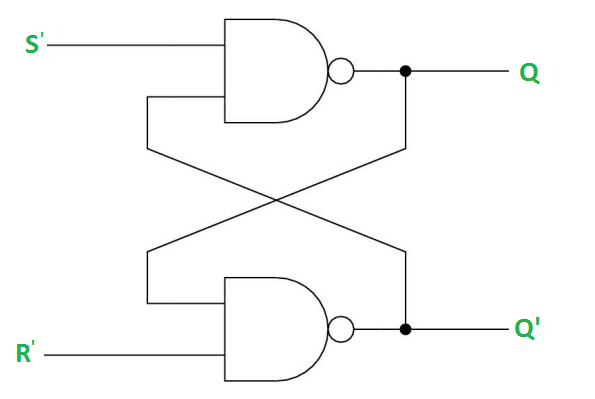

Logica-diagram van S-R Latch

De SR -vergrendeling is een basale sequentieel logische circuit met twee hoofdconfiguraties: NOR of NAND -poorten.Elke installatie beïnvloedt hoe de vergrendeling werkt en reageert op ingangen, waardoor aanpassing voor verschillende elektronische toepassingen mogelijk is.

Afbeelding 8: Logisch diagram vertegenwoordigt de S-R-latch met behulp van NAND Gate

Implementatie met behulp van NAND Gates

Bij het bouwen van een SR -vergrendeling met NAND -poorten wordt een feedbacklus gebruikt om zijn staat te behouden.Met deze opstelling kan de vergrendeling zijn vorige status behouden wanneer beide ingangen (S en R) laag zijn.NAND Gates Output High tenzij beide ingangen hoog zijn.De status van de vergrendeling verandert wanneer de ene input hoog is en de andere laag is.Het is het beste om te voorkomen dat zowel S als R tegelijkertijd hoog instelt, omdat dit beide uitgangen laag dwingt om laag te gaan, wat leidt tot een niet -gedefinieerde toestand waar de uitgangen niet langer complementair zijn.Juiste invoerbeheer is een must om instabiliteit in NAND-gebaseerde SR-vergrendelingen te voorkomen.

Implementatie met behulp van noch poorten

Het gebruik van noch poorten voor een SR -vergrendeling verandert de operationele omstandigheden in vergelijking met NAND Gates.In deze configuratie houdt de vergrendeling zijn status vast wanneer beide ingangen hoog zijn.De vergrendeling verandert status wanneer de ene input laag is en de andere hoog is.Noch poorten output alleen hoog als beide ingangen laag zijn.Deze opstelling is nuttig in circuits waarbij de standaardstatus beide uitgangen laag moet hebben, waardoor voorspelbare uitgang onder hoge inputomstandigheden wordt gewaarborgd.Het is echter het beste om te voorkomen dat beide ingangen tegelijkertijd laag instellen, omdat dit tegenstrijdige uitgangen veroorzaakt en de betrouwbaarheid van de vergrendeling vermindert.

Figuur 9: Logisch diagram vertegenwoordigt S-R-latch met behulp van NOR-poort

Voorbeeldcircuit

Onderzoek naar hoe SR -vergrendelingen in het echte leven werken, toont hun nut.Een goed voorbeeld is een circuit met behulp van de CD4001 -chip, die vier noch poorten heeft.Dit circuit laat zien hoe SR -vergrendelingen apparaten zoals LED's kunnen besturen met eenvoudige acties zoals op knoppen drukken.

In dit voorbeeld zijn de NOR -poorten in de CD4001 -chip ingesteld om een SR -vergrendeling te maken.Twee poorten zijn verbonden in een feedbacklus om de vergrendelingstoestand te behouden.Pushbuttons worden aan het circuit toegevoegd als ingangen voor set en reset.Als u op een knop drukt, wordt de status van de invoer gewijzigd, die de vergrendeling en de LED -status verandert.Als u bijvoorbeeld op de set -knop op de LED ligt en deze verlicht blijft, zelfs nadat de knop is vrijgegeven, laat zien hoe de vergrendeling een status kan behouden.

Om het circuit beter te maken, kunnen meer LED's worden toegevoegd om de uitgangsstatus van zowel Q als Q-Bar weer te geven.Dit maakt het gemakkelijker om te zien hoe de vergrendeling werkt, wat zeer nuttig is in leeromgevingen.

Afbeelding 10: S-R Latch met behulp van de CD4001-chip

Code -implementatie

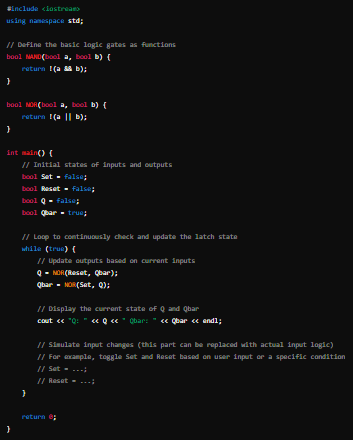

Het vertalen van de operationele logica van een SR -vergrendeling in software laat zien hoe digitaal logisch ontwerp zowel in hardware als in virtuele simulaties kan werken.Het gebruik van een programmeertaal zoals C ++ is effectief omdat het de complexe logica en controle ondersteunt die nodig is om hardwaregedrag te imiteren.

Om een SR -vergrendeling in C ++ te maken, begint u met het definiëren van de basislogische poorten als functies die werken als hun hardwareversies.Een NAND -poortfunctie zou bijvoorbeeld het tegenovergestelde van de en bewerking op zijn ingangen retourneren.Evenzo zou een NOR -poortfunctie het tegenovergestelde van de OK -bewerking retourneren.Met deze basisfuncties kunt u het gedrag van de SR -vergrendeling modelleren door een feedbacklus tussen deze poortfuncties te maken, gebaseerd op het circuitschema van de vergrendeling.

De code zou meestal een lus hebben die continu de staten van de ingangen controleert (ingesteld en reset) en de uitgangen (Q en Q-Bar) dienovereenkomstig bijwerken.Voorwaardelijke uitspraken in deze lus bepalen hoe veranderingen in de input de uitgangen beïnvloeden, waardoor het fysieke gedrag van de SR -vergrendeling nauw nadenkt.Als bijvoorbeeld zowel ingestelde als reset ingangen laag zijn, blijven de uitgangen hetzelfde.Als de set hoog is en de reset laag is, wordt de uitgang Q hoog en wordt de Q-bar laag, waardoor de ingestelde staat van de vergrendeling wordt gerepliceerd.

Hier is een eenvoudig voorbeeld van hoe dit eruit kan zien in code:

Figuur 11: SR -vergrendeling in C ++

Deze code stelt een eenvoudige SR -vergrendeling in met behulp van nor -poorten en controleert en werkt continu de vergrendelingstoestand op op basis van de invoer.

Toepassingen van de SR -vergrendeling

Besturingssystemen bij motorbewerkingen: de SR -vergrendeling vereist door systemen voor motorbesturingselement.Met behulp van Start (S) en Stop (R) drukknopschakelaars, houdt de SR -vergrendeling een motor draaiende, zelfs nadat de startknop is vrijgegeven.Deze opstelling zorgt ervoor dat de motor continu loopt totdat het is gestopt en de veiligheid en gemak verbetert.

Geheugen- en gegevensopslag: bij het maken van grotere geheugencircuits speelt de SR -vergrendeling een rol, omdat deze een enkel beetje gegevens kan opslaan.Het handhaaft gegevens in een stabiele toestand totdat het bijgewerkt is en vormt de basis van geheugencellen in digitaal computergebruik.

Signaalbesturing en beheer: in controlesignaaltoepassingen bevatten SR -vergrendelingen specifieke bits totdat aan bepaalde voorwaarden is voldaan, waardoor de juiste volgorde en timing in bewerkingen wordt gewaarborgd.Precisie in signaalverwerking en gegevensstroom hangt hiervan af.

Debouncingcircuits: SR -vergrendeling stabiliseren signalen van mechanische schakelaars en knoppen, waardoor valse triggering en fouten worden veroorzaakt die worden veroorzaakt door de "bounce" wanneer schakelaars worden ingedrukt.Dit past vooral in digitale interfaces zoals toetsenborden.

Fundamentele elementen in digitale systemen: het ontwerp van flip-flops en tellers, die geschikt zijn voor timing en sequencing in elektronica, is sterk afhankelijk van SR-vergrendelingen.Ze worden ook gebruikt als pulsvergrendelingen voor het schakelen van snelle toestand.

Gespecialiseerde toepassingen: in asynchrone systemen worden variaties zoals de D -vergrendeling gebruikt voor veilige en betrouwbare gegevensoverdracht.In synchrone tweefasensystemen verminderen gegevensvergrendelingen het aantal doorvoer, waardoor de efficiëntie wordt verbeterd en de vertraging vermindert.

Bredere Implications in Electronics: SR -vergrendelingen worden op grote schaal gebruikt in vermogenscircuits en spelen een rol in energiebesparing binnen elektronische apparaten.Ze beheren stroomstaten op een gedetailleerd niveau, wat bijdraagt aan de algehele energie -efficiëntie van digitale systemen.

Conclusie

De S-R-gatch toont het belang van eenvoudige logische structuren in complexe digitale systemen.Door naar de verschillende setups te kijken en hoe het werkt, zien we dat de S-R-latch gegevens stabiel houdt en systemen efficiënt en betrouwbaar maakt.Het kan onder verschillende omstandigheden werken, aangetoond door waarheidstabellen en logische diagrammen, waardoor het zich kan aanpassen voor verschillende toepassingen, van motorbesturingselement tot basisditale circuits zoals flip-flops en tellers.De S-R-latch is geschikt in veel praktische toepassingen, zoals geheugencellen in computers en het ontwerpen van circuits in digitale interfaces, het verbeteren van de efficiëntie en het verminderen van fouten in elektronische apparaten.Met feedbackmechanismen en zorgvuldige invoersignaalbeheer is de S-R-latch goed voor het ontwerpen van betrouwbaardere en efficiënte digitale systemen.Het bestuderen van de functie ervan via softwaresimulaties helpt de theoretische elektronica te verbinden met echte toepassingen, waardoor de S-R-Latch een belangrijk onderwerp is voor zowel nieuwe als ervaren elektronische ingenieurs.

Veelgestelde vragen [FAQ]

1. Wat is het doel van de SR -vergrendeling?

De SR -vergrendeling wordt gebruikt om een beetje gegevens op te slaan;Het is een basisvorm van geheugen in digitale circuits.De belangrijkste functie is om de status van een beetje te behouden totdat deze wordt gewijzigd door invoersignalen.

2. Is SR Latch actief hoog of laag?

De SR -vergrendeling is meestal actief hoog, wat betekent dat deze reageert op hoge ingangen (logisch niveau 1).Wanneer de ingangen s (set) en r (reset) hoog zijn, activeren ze veranderingen in de uitgang.

3. Wat is het nadeel met een SR -vergrendeling?

Een groot nadeel van de SR -vergrendeling is de gevoeligheid voor een ongeldige toestand waarbij zowel de set- als de reset -ingangen tegelijkertijd hoog zijn.Deze situatie leidt tot een ongedefinieerde output, wat kan leiden tot onbetrouwbaar of onvoorspelbaar gedrag.

4. Wat zijn de regels voor de SR -vergrendeling?

Als S (set) hoog is en R (reset) laag is, is de uitgang Q ingesteld op hoog.

Als R hoog is en S laag is, wordt de uitgang Q gereset naar laag.

Als zowel S als R laag zijn, behoudt de uitgang zijn vorige status.

Als zowel S als R hoog zijn, is de uitgang niet gedefinieerd of ongeldig.

5. Wat is het geheugen in SR Latch?

Het geheugen in een SR -vergrendeling verwijst naar zijn vermogen om de uitgangsstatus (hoog of laag) voor onbepaalde tijd te handhaven, totdat het input ontvangt om de status te wijzigen.Dit maakt het een bistabiel apparaat, ideaal voor eenvoudige geheugenopslag.

6. Wat zijn de uitgangen van de SR -vergrendeling?

De SR-vergrendeling heeft twee uitgangen, Q en Q '(Q-Bar).Q vertegenwoordigt de huidige toestand, terwijl Q 'het omgekeerde van Q is. Wanneer Q hoog is, is Q' laag en vice versa.

7. Waar gebruiken we Latch?

Wanneer gegevensopslag op korte termijn of het bewaren van de staat vereist zijn, worden vergrendeling in verschillende soorten toepassingen gebruikt.Dit omvat gegevensopslag in flip-flops, registers en geheugeneenheden, evenals in systemen die gegevenssynchronisatie en circuithold-functies vereisen.