SR -vergrendelingen beheersen: symbolen, functies en praktische toepassingen

Een SR -vergrendeling is een asynchroon circuit dat onafhankelijk van kloksignalen werkt, waardoor het een veelzijdig hulpmiddel is in verschillende toepassingen.Het onderhoudt een binaire toestand - ofwel hoog (1) of laag (0) - en kan een enkel beetje informatie opslaan, die het bevat totdat nieuwe invoersignalen een wijziging bepalen.Dit eenvoudige binaire opslagelement is geconstrueerd met behulp van twee gekoppelde logische poorten, meestal Nor of NAND-poorten.De ingestelde ingang (s) activeert de vergrendeling, waarbij de uitgang (Q) op hoog wordt ingesteld, terwijl de reset -ingang (R) de uitgang laag instelt.Gelijktijdige hoge signalen op beide ingangen leiden echter tot een niet -gedefinieerde toestand, een toestandsontwerpers moeten vermijden.SR -vergrendelingen zijn niet alleen theoretische constructen;Ze worden geïmplementeerd in praktische systemen om tijdelijke gegevens te bevatten, intermediaire verwerkingsresultaten te ondersteunen en zelfs foutdetectie te beheren in kritieke toepassingen zoals ruimtevaart- en medische hulpmiddelen, die hun onmisbaarheid in het ontwerp van digitaal circuit tonen.Catalogus

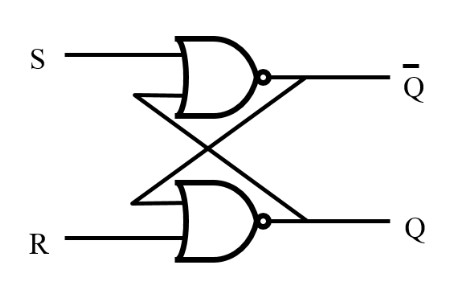

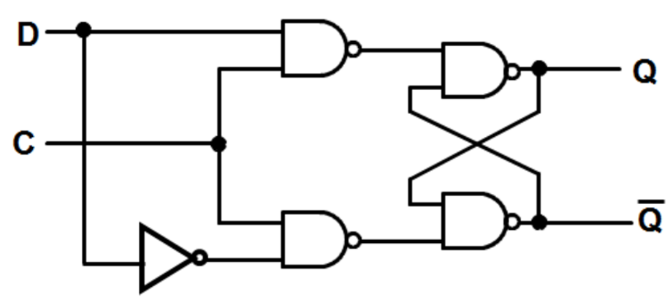

Figuur 1: SR -vergrendeling

Wat is een SR -vergrendeling?

Een SR-vergrendeling, of set-reset vergrendeling, is een eenvoudig binair opslagelement dat tot de categorie asynchrone circuits behoort.In tegenstelling tot synchrone circuits werken SR -vergrendelingen zonder een kloksignaal en vertrouwen ze uitsluitend op de directe controle van ingangssignalen.Hierdoor kunnen ze onafhankelijk functioneren binnen digitale circuits.Een SR -vergrendeling kan twee stabiele toestanden handhaven: hoog (1) en laag (0), waardoor het een enkel beetje informatie kan opslaan totdat deze wordt bijgewerkt door nieuwe invoersignalen.

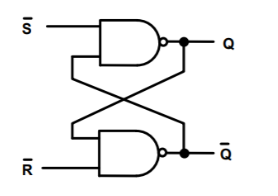

Het construeren van een SR-vergrendeling omvat meestal twee kruiskoppelde logische poorten, gewoonlijk noch poorten of NAND-poorten.In een SR -vergrendelingsontwerp met behulp van NOR -poorten is de uitgang van elke poort verbonden met de invoer van de andere, waardoor een feedbacklus wordt gevormd.Deze configuratie zorgt ervoor dat de vergrendeling van toestand kan veranderen op basis van de invoersignalen met behoud van stabiliteit totdat een nieuwe invoer een wijziging aanspoort.

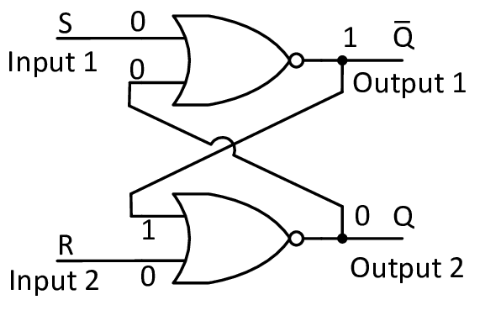

Figuur 2: SR -vergrendeling (2)

Stel ingang (s) in: wanneer de ingestelde ingang (s) wordt geactiveerd (hoog), schakelt de vergrendelinguitgang (Q) over naar hoog (1).

Reset ingang (R): wanneer de reset -ingang (R) wordt geactiveerd (hoog), schakelt de uitgang (Q) over naar laag (0).

Beide ingangen hoog: als zowel S- als R -ingangen gelijktijdig hoog zijn, komt de vergrendeling in een ongedefinieerde toestand, die in het ontwerp moet worden vermeden.

SR -vergrendelingen zijn essentieel voor tijdelijke gegevensopslag en tussenliggende resultaat in digitale systemen.Het zijn de fundamentele elementen in meer complexe sequentiële circuits zoals multi-bit shift-registers, geheugeneenheden en bepaalde soorten tellers.

In deze toepassingen bieden SR -vergrendelingen stabiele gegevensbehoud en kunnen ze snel reageren op veranderingen in externe signalen, waardoor de efficiënte werking van het gehele elektronische systeem wordt gewaarborgd.

Een andere kritieke toepassing van SR -vergrendelingen is in foutdetectie en correctielogica binnen digitale circuits.Vanwege hun vermogen om een stabiele toestand vast te houden, kunnen ze de systeemstatuswijzigingen volgen en snel terugkeren naar een vooraf gedefinieerde veilige status bij het detecteren van een afwijking.Deze functie is met name waardevol in systemen met hoge betrouwbaarheid zoals ruimtevaart en medische hulpmiddelen.

Symbool van de SR -vergrendeling

Het begrijpen van zijn symbool en structuur is van fundamenteel belang om de werking en praktisch gebruik ervan te begrijpen.In circuitdiagrammen heeft de SR -vergrendeling meestal twee hoofdinvoerpoorten met het label S (set) en R (reset).Deze ingangen regelen de uitgangsstatus van de vergrendeling, meestal weergegeven als Q. Sommige ontwerpen hebben ook de inverse output, gelabelde Q ', die de tegenovergestelde status van Q biedt.

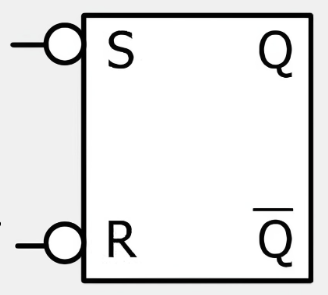

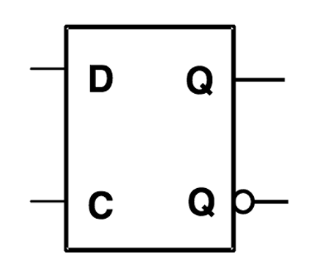

Figuur 3: Symbool van de SR -vergrendeling

Een SR -vergrendeling wordt vaak weergegeven door een rechthoekig symbool met ingangen S en R en een uitgang Q. In sommige gevallen wordt de uitgang q 'ook getoond.Met deze duidelijke labeling kunnen circuitontwerpers snel de functie van de component identificeren en de rol ervan binnen het grotere circuit.

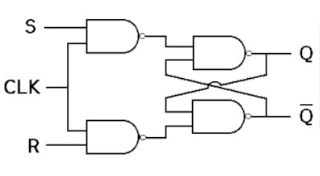

Een gemeenschappelijke variant van de SR -vergrendeling omvat een klok (CLK) -invoer.De CLK -input zorgt ervoor dat toestandsveranderingen in synchronisatie optreden met het kloksignaal, waardoor precieze timingregeling mogelijk is.In deze opstelling, zelfs als S of R wordt geactiveerd, wordt de status van de vergrendeling alleen bijgewerkt wanneer het CLK -signaal voldoet aan specifieke voorwaarden, meestal op de stijgende of dalende rand.Dit voorkomt fouten veroorzaakt door ingangssignaal glitches of onbedoelde veranderingen.

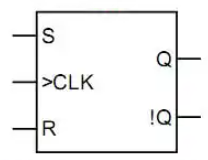

Figuur 4: Symbool van de klokafwijking SR-vergrendeling

Het geklokte SR -vergrendelingssymbool bevat de S-, R- en CLK -ingangen in een rechthoek.Deze gestandaardiseerde weergave helpt ontwerpers de functionaliteit van de vergrendeling en de timingvereisten te begrijpen.In krachtige computergebruik of complexe gegevensoverdrachtsystemen, zorgt zorgvuldige CLK-besturingselementen bijvoorbeeld ervoor dat gegevens worden opgeslagen en nauwkeurig worden overgedragen in elke verwerkingsfase, waardoor de algehele systeemprestaties en betrouwbaarheid worden geoptimaliseerd.

Nauwkeurige controle van SR-vergrendelingsingangen is belangrijk, met name bij het ontwerpen van geheugen met hoge snelheid en grote capaciteit of tijdelijke databuffers.Door logische circuits te ontwerpen om S- en R -activering te beheren, kunnen complexe functies zoals gegevenslaading, wissen of toestand worden bereikt.Nauwkeurige CLK -signaalregeling zorgt ervoor dat alle gegevensbewerkingen een vooraf gedefinieerde timingsequentie volgen, waardoor de systeemefficiëntie en gegevensverwerkingsmogelijkheden aanzienlijk worden verbeterd.

Een diep begrip van het symbool en de structuur van de SR -vergrendeling helpt niet alleen bij het correct circuitontwerp en probleemoplossing, maar ook bij het uitvoeren van complexe digitale logische bewerkingen en het verbeteren van de systeemprestaties.Dit is vooral van cruciaal belang in toepassingen die een hoge betrouwbaarheid en precieze controle vereisen, zoals ruimtevaart- en medische hulpmiddelen.

Soorten vergrendeling en hun werkprincipes

Vergrendeling zijn fundamentele componenten in elektronisch ontwerp en bieden verschillende functies en brede toepassingen.De belangrijkste soorten vergrendeling zijn SR -vergrendeling en D -vergrendelingen, elk met unieke bewerkingen en use cases.

SR -vergrendeling

De SR-vergrendeling, of set-reset latch, is een basisopslagapparaat bestuurd door de twee ingangen, s (set) en r (reset).

Wanneer de S -invoer een hoog signaal ontvangt, wordt de uitgang Q hoog, wat aangeeft dat de gegevens zijn ingesteld.Wanneer de R -ingang een hoog signaal ontvangt, wordt de uitgang Q laag, wat aangeeft dat de gegevens worden gereset.Als zowel S- als R -ingangen gelijktijdig hoog zijn, komt de vergrendeling in een ongedefinieerde toestand, waardoor potentiële uitgangsinstabiliteit wordt veroorzaakt.Deze toestand moet in het ontwerp worden vermeden.De directe respons van de SR Latch op invoersignalen maakt het nuttig in situaties die een snelle reactie vereisen.

D -vergrendeling

De D -vergrendeling, ook bekend als een gegevensvergrendeling of transparante vergrendeling, biedt meer complexe controle met gegevensinvoer D en kloksignaal CLK.

Figuur 5: D Latch

Figuur 6: D Latch Symbol

Wanneer CLK hoog is, volgt de uitvoer Q de invoer D, waardoor gegevens vrij kunnen doorgaan.Wanneer CLK laag wordt, wordt de stroomwaarde van D vergrendeld en blijft de uitgang Q constant tot het volgende clk hoge signaal.Dit mechanisme maakt de D -vergrendeling ideaal om gegevens tijdelijk op te slaan om verschillende verwerkingssnelheden binnen een systeem te synchroniseren.

SR- en D -vergrendelingen spelen een ongeëvenaarde rol bij gegevensopslag en logica van de statusmachines.Vanwege hun directe respons op ingangsniveau zijn vergrendelingen essentieel bij het ontwerpen van asynchrone circuits.Ze bieden essentiële functies voor complexe gegevenstransfers en energiebeheersystemen, waardoor de staatsinformatie effectief wordt opgeslagen om een stabiele werking te garanderen.Goed gebruik van deze vergrendelingen kan de betrouwbaarheid en efficiëntie van de circuit aanzienlijk verbeteren, waardoor ze onmisbaar zijn in moderne elektronische systemen.

Waarheidstabel van een SR -vergrendeling

Figuur 7: Sr Nand Latch

|

S |

R |

Q |

Q' |

Opmerking |

|

0 |

0 |

1 |

1 |

VERBODEN |

|

0 |

1 |

1 |

0 |

SET |

|

1 |

0 |

0 |

1 |

Reset |

|

1 |

1 |

Q |

Q' |

BEHOUDEN |

Grafiek 1: waarheidstabel van SR -vergrendeling met behulp van NAND -poorten

Figuur 8: SR Nor Latch

|

S |

R |

Q |

Q' |

Opmerking |

|

0 |

0 |

Q |

Q' |

BEHOUDEN |

|

0 |

1 |

1 |

0 |

Reset |

|

1 |

0 |

0 |

1 |

SET |

|

1 |

1 |

0 |

0 |

VERBODEN |

Grafiek 2: waarheidstabel van SR Latch met behulp van noch poorten

Nu nemen we de waarheidstabel van de SR -vergrendeling met behulp van nor -poort als een voorbeeld om de betekenis van de waarheidstabel van de SR -vergrendeling te begrijpen.

Input- en uitvoertoestanden

Zowel S als R zijn 0: de vergrendeling blijft in zijn huidige status.De uitgang Q blijft hetzelfde, of het nu 0 of 1 is.

S is 0 en R is 1: de vergrendeling wordt gereset, waardoor de uitgang Q naar 0 wordt gedwongen.

S is 1 en R is 0: de vergrendelingssets, waardoor de uitgang Q gelijk is aan 1.

Zowel S en R zijn 1: deze voorwaarde is ongeldig of ongedefinieerd, vaak aangeduid als de "verboden" staat in een SR -vergrendeling.In dit geval zijn Q en Q 'beide gelijk aan 0, wat leidt tot een dubbelzinnige output.

Wanneer S en R allebei 0 zijn, doet de vergrendeling niets en houdt gewoon zijn huidige waarde vast.Dit is handig om de staat te onderhouden zonder wijzigingen.

Wanneer S 0 is en R 1 is, wordt de vergrendeling expliciet verteld om te resetten, waardoor Q 0 is, ongeacht de vorige status.Dit is een eenvoudige manier om de vergrendeling te wissen.

Wanneer S 1 is en R 0 is, wordt de vergrendeling ingesteld, waardoor Q wordt gewaarborgd. Dit is hoe u een '1' opslaat in de vergrendeling.

Wanneer S en R beide 1 zijn, is de status niet toegestaan omdat deze ervoor zorgt dat beide uitgangen 0 zijn, wat tegenstrijdig en onbetrouwbaar is.Ontwerpers moeten deze toestand vermijden om een stabiele werking te garanderen.

Voor- en nadelen van vergrendelingen

Vergrendeling worden veel gebruikt in het ontwerp van het digitale circuit vanwege hun eenvoud en lage kosten.Deze kenmerken stellen vergrendeling in staat om op hoge snelheden te werken met een laag stroomverbruik, waardoor ze ideaal zijn voor digitale systemen met hoge snelheid.In processorregisterbestanden kunnen vergrendelingen bijvoorbeeld snel gegevens opslaan en ophalen, waardoor de verwerkingssnelheid en efficiëntie aanzienlijk worden verhoogd.

Voordelen van vergrendelingen

Eenvoud en kosteneffectiviteit: vergrendelingen zijn eenvoudige componenten die goedkoop zijn om te implementeren in digitale circuits.

Hoge snelheid en laag vermogen: hun ontwerp zorgt voor een snelle werking met minimaal stroomverbruik, wat cruciaal is in digitale systemen met hoge snelheid.

Efficiëntie in gegevensverwerking: in applicaties zoals processorregisterbestanden bieden vergrendelingen snelle gegevensopslag en ophalen, waardoor de algehele systeemprestaties worden verbeterd.

Nadelen van vergrendelingen

Ondanks hun voordelen hebben vergrendelingen opmerkelijke beperkingen in bepaalde ontwerpen en toepassingen.

Onvoorspelbaar gedrag in asynchrone ontwerpen: zonder klok signaalregeling kunnen vergrendelingen zich onvoorspelbaar gedragen.In SR -vergrendelingen, als zowel set (s) als reset (R) ingangen gelijktijdig hoog zijn, wordt de uitgang ongedefinieerd, wat leidt tot instabiliteit.Dit is problematisch in realtime controle of veiligheidskritische toepassingen, waarbij betrouwbare output cruciaal is.

Complex timingontwerp: ontwerpen met vergrendelingen vereist zorgvuldige timingoverwegingen.Ingenieurs moeten rekening houden met de vertragingen van de signaalver voortplanting en raceomstandigheden om timingfouten te voorkomen.Onjuist ontwerp kan resulteren in gegevensveranderingen voordat het kloksignaal stabiliseert, waardoor gegevenscorruptie of onjuiste gegevensverzameling worden veroorzaakt.Dit vereist een diep begrip van timinganalyse en circuitgedrag.

Om deze uitdagingen aan te gaan, kunnen specifieke ontwerptechnieken en strategieën worden gebruikt:

Synchronisatiemechanismen: het toevoegen van synchronisatiemechanismen kunnen helpen bij het beheren van asynchrone inputs en het verminderen van onvoorspelbaar gedrag.

Aangepast klokbeheer: het implementeren van aangepaste strategieën voor klokbeheer kan ervoor zorgen dat gegevens correct en op het juiste moment worden vergrendeld.

Gebruik van EDA -tools: Modern Electronic Design Automation (EDA) Tools bieden geavanceerde analyse- en optimalisatiemogelijkheden.Deze tools helpen bij het voorspellen en oplossen van timing- en synchronisatieproblemen tijdens de ontwerpfase, waardoor de betrouwbaarheid en prestaties van digitale systemen worden verbeterd met behulp van vergrendelingen.Ze helpen ontwerpers bij het vroegtijdig identificeren van potentiële problemen, waardoor het eindproduct betrouwbaar werkt onder verschillende omstandigheden.

Praktische toepassingen van SR -vergrendelingen

SR -vergrendelingen, bekend om hun vermogen om snel en betrouwbaar de staat te behouden, worden veel gebruikt in verschillende elektronische systemen.Ze blinken uit in scenario's die tijdelijke gegevensopslag of staatsbehoud vereisen.

Tijdelijke gegevensopslag

SR -vergrendelingen worden vaak gebruikt in het cachegeheugen om gegevens tijdelijk op te slaan.Hierdoor kan het systeem snel toegang krijgen tot vaak gebruikte gegevens, waardoor de gegevensverwerkingsmogelijkheden en de efficiëntie van grootschalige processors aanzienlijk worden gestimuleerd.

Opslagregisterbestanden

In processors maken SR -vergrendelingen snelle opslag en het ophalen van gegevens in registerbestanden, waardoor de verwerkingssnelheid en de algehele systeemprestaties worden verbeterd.

Controlssignalen handhaven

In digitale besturingssystemen zijn SR -vergrendelingen nuttig bij het handhaven van de status van bepaalde besturingssignalen totdat externe omstandigheden of systeemlogica een wijziging bepaalt.Ook helpen ze bij het behouden van staten binnen het systeem, waardoor consistente prestaties worden gewaarborgd in bewerkingen die precisie en betrouwbaarheid vereisen.

Trigger- en tegencircuits

Op SR-latch gebaseerde flip-flops worden vaak gebruikt in circuits die gesynchroniseerde werking vereisen, zoals digitale klokken en timers.Ze regelen telpulsen en zorgen voor nauwkeurige tijdwaarneming en betrouwbare prestaties.Deze circuits zijn afhankelijk van SR -vergrendelingen om nauwkeurige tellingen te handhaven, wat timing en sequencing in digitale systemen vergemakkelijkt.

Mechanische interacties

SR -vergrendelingen zijn effectief bij het elimineren van mechanische stuitering in schakelaars.Een mechanische bounce treedt op wanneer een schakelaar snel, repetitief signaal verandert vanwege slecht contact.SR -vergrendeling stabiliseert het uitgangssignaal, waardoor fouten worden veroorzaakt veroorzaakt door lawaaierige signalen.

SR flip-flop

Een SR-flip-flop, vaak een rand-geactiveerde set-reset flip-flop genoemd, bestaat uit twee onderling verbonden SR-vergrendeling.Door deze dual-latch-structuur kan het reageren op specifieke klokranden van de kloksignaal (stijgend of dalen) om zijn status te veranderen.Dit wordt bereikt door speciale logische controle tussen de vergrendelingen.De uitgang van de eerste grendel wordt onderdeel van de invoer voor de tweede vergrendeling, en de uitgang van de tweede vergrendeling beïnvloedt op zijn beurt de eerste vergrendeling, waardoor een in elkaar grijpende feedback -lus ontstaat.

Figuur 7: SR flip-flop

De SR flip-flop verandert van status precies bij de stijgende of dalende rand van het kloksignaal.De in elkaar grijpende feedback tussen de twee SR-vergrendelingen zorgt ervoor dat de flip-flop alleen van status verandert in reactie op de klokrand, waardoor stabiele en betrouwbare output biedt.

In microprocessors en digitale signaalprocessors worden SR-flip-flops gebruikt voor gegevensbemonstering en -opslag.Ze leggen gegevens vast en stabiliseren bij gespecificeerde klokranden en zorgen voor betrouwbare latere gegevensverwerking en -analyse.

Het rand-triggerende mechanisme helpt raceomstandigheden te voorkomen, waarbij verschillende delen van het circuit tegelijkertijd van status kunnen veranderen zonder synchronisatie, wat mogelijk resulteert in onstabiele of onjuiste uitgangen.SR flip-flops zijn cruciaal bij het implementeren van specifieke communicatieprotocollogica, zoals framesynchronisatie en foutdetectie.Hun stabiliteit en snelle responstijd helpen bij het handhaven van de kwaliteit van de gegevensoverdracht en de betrouwbaarheid van het systeem.

Verboden Staten in SR-vergrendelingen en SR-flip-flops

Bij het ontwerpen van SR-vergrendelingen en SR-flip-flops met behulp van NAND en NOR-poorten, moeten we allemaal aandacht besteden aan het beheren en vermijden van geremde staten.Een verboden toestand treedt op wanneer zowel de set (s) als reset (R) ingangen tegelijkertijd hoog zijn (voor NAND -poorten) of laag (voor noch poorten).Deze combinatie leidt tot een onbepaalde uitgangsstatus, omdat de uitgang afhangt van de vorige toestand van het circuit, waardoor het onvoorspelbaar is.

Verboden Staten in Nand Gate SR -vergrendelingen

Wanneer zowel S als R laag zijn, worden beide uitgangen hoog, wat de complementaire uitvoerkarakteristiek van de vergrendeling schendt.Dit resulteert in een onbepaalde toestand.

Verboden Staten in Nor Gate SR -vergrendelingen

Wanneer zowel S als R hoog zijn, worden beide uitgangen laag, waardoor ook een onbepaalde toestand ontstaat.Dit kan leiden tot onvoorspelbaar gedrag in het circuit.

Praktische benaderingen om verboden staten te vermijden

Besturingslogica toevoegen

Gebruik extra logische poorten om de toestanden van S en R te controleren. Als beide ingangen trend naar een verboden toestand, aanpassen, pas dan automatisch een input aan om de onbepaalde toestand te voorkomen.Dit zorgt ervoor dat de uitgangen stabiel en voorspelbaar blijven.Implementeer een logische poort die tussenbeide komt wanneer S en R beide hoog (of laag) zijn en een input aanpassen om een geldige status te behouden.

Softwaresimulatie en hardwaretests

Voer grondige softwaresimulaties uit om potentiële verboden toestanden te identificeren onder verschillende bedrijfsomstandigheden.Hierdoor kunnen ontwerpers logische fouten zien en corrigeren vóór fysieke implementatie.Voer uitgebreide hardwaretests uit om te valideren dat het circuit alle invoercombinaties correct verwerkt.Deze stap helpt ervoor te zorgen dat de vergrendeling of flip-flop betrouwbaar werkt in real-world scenario's.

Conclusie

De veelzijdigheid en betrouwbaarheid van SR -vergrendeling onderstrepen hun betekenis in het ontwerp van het digitale circuit.Door het genuanceerde gedrag van SR -vergrendelingen te verkennen via hun symboolrepresentaties, waarheidstabellen en praktische toepassingen, krijgen we een volledig inzicht in hun werking en belang.Ondanks de potentiële valkuilen van niet -gedefinieerde toestanden in asynchrone ontwerpen, kan strategische implementatie van controlelogica en uitgebreide simulatie deze risico's verminderen.Geavanceerde elektronische ontwerpautomatisering (EDA) Tools verbeteren verder de betrouwbaarheid en prestaties van circuits met SR -vergrendeling door timing- en synchronisatieproblemen te voorspellen en op te lossen.Of het nu wordt gebruikt bij tijdelijke gegevensopslag, onderhoud van het besturingssignaal of foutdetectie, SR -vergrendelingen blijken fundamenteel te zijn bij het creëren van robuuste en efficiënte digitale systemen.Hun rol in snelle geheugenbewerkingen en synchrone gegevensverwerking in complexe toepassingen is een voorbeeld van hun blijvende relevantie.Naarmate de technologie vordert, blijven de principes voor SR -vergrendelingen innovaties in de digitale elektronica informeren en inspireren, zodat deze elementaire componenten integraal blijven voor de ontwikkeling van geavanceerde en betrouwbare elektronische apparaten.

Veelgestelde vragen [FAQ]

1. Wat is een SR -vergrendeling?

Een SR-vergrendeling of set-reset-vergrendeling, is een fundamenteel binair opslagelement dat wordt gebruikt in digitale circuits.Het is een asynchrone circuit, wat betekent dat het zonder kloksignaal werkt, die afhankelijk is van de directe controle van de ingangen om toestand te veranderen.

2. Wat is de functie van SR in logica?

In logica regelen de SR (set-reset) ingangen de status van de vergrendeling.

3. Welk type logische poort gebruikt een SR -vergrendeling?

Een SR -vergrendeling gebruikt meestal noch poorten of NAND -poorten.In een NOR-poort-gebaseerde SR-vergrendeling wordt de uitvoer van elke NOR-poort teruggevoerd in de invoer van de andere, waardoor een stabiele feedback-lus wordt gecreëerd.In een op NAND GATE gebaseerde SR-vergrendeling wordt een vergelijkbare feedbackconfiguratie gebruikt, maar de logische niveaus worden omgekeerd in vergelijking met de NOR-gate-gebaseerde vergrendeling.Beide configuraties bereiken dezelfde basisfunctionaliteit als het handhaven van een binaire toestand op basis van de set- en reset -ingangen.

4. Hoe werkt een vergrendeling?

Een vergrendeling werkt door feedback te gebruiken om zijn uitvoerstatus te behouden op basis van de ingeboden invoer.In een SR -vergrendeling regelen de set (s) en reset (r) ingangen de status van de uitgang (q).Wanneer de ingestelde ingang wordt geactiveerd (hoog), wordt de uitgang ingesteld op hoog (1).Wanneer de reset -ingang wordt geactiveerd (hoog), wordt de uitgang gereset naar laag (0).De feedbacklus in het ontwerp van de grendel zorgt ervoor dat zodra een uitgangsstatus is vastgesteld, deze stabiel blijft totdat een nieuw ingangssignaal het verandert.

5. Wat is het nadeel met een SR -vergrendeling?

Het primaire nadeel van een SR -vergrendeling is de niet -gedefinieerde toestand die optreedt wanneer zowel set (s) als reset (r) ingangen gelijktijdig hoog zijn.Deze voorwaarde leidt tot een onbepaalde uitgangsstatus, die instabiliteit en onvoorspelbaar gedrag in digitale circuits kan veroorzaken.Deze "verboden" toestand moet in het ontwerp worden vermeden om een betrouwbare werking te garanderen.

SR LATCH, SET-RESET-LATCH, ASYNCHRONE CIRCUIT, BINAIRE OPSLAGENDELEMENT, Digitale circuits, noch poorten, NAND-poorten, feedbacklus, hoge toestand, lage toestand, niet-gedefinieerde toestand, kloksignaal, directe controle, tijdelijke gegevensopslag, tussenliggende resultaat, het tussenliggende resultaat,Foutdetectie, ruimtevaarttoepassingen, medische hulpmiddelen, circuitontwerp, geklokte SR-vergrendeling, invoersignalen, symbool en structuur, high-speed geheugen, gegevensbuffers, timingcontrole, precieze controle, toestandsretentie, microprocessors, digitale signaalprocessors, gegevensbemonstering, gegevensOpslag, rand-triggered, SR Flip-Flop, in elkaar grijpende feedback, raceomstandigheden, communicatieprotocol logica, frame-synchronisatie, foutdetectie, signaal glitches, elektronische ontwerpautomatisering, EDA-tools, synchronisatiemechanismen, aangepast klokbeheer, timingfouten, propagatie-vertragingen,Raceomstandigheden, complexe gegevensoverdrachten, energiebeheersystemen, mechanische bounce, praktische toepassingen, digitale besturingssystemen, logische poorten, softwaresimulaties, hardwaretests, verboden toestanden, betrouwbaarheid van de vergrendeling.