Innovatieve gids voor JK-flip-flops: analyse van waarheidstabellen, mechanismen en strategische toepassingen

Dit artikel onderzoekt de architectuur, werking en diverse toepassingen van de JK Flip-Flop, beginnend bij de basisstructuur en input-outputrelaties, via gedetailleerde operationele mechanica, tot zijn strategische implementaties in complexe digitale systemen.Het discours strekt zich uit tot onderscheid tussen de door rand getriggerde en level-geactiveerde varianten, waardoor hun respectieve hulpprogramma's in synchrone en asynchrone omgevingen worden geanalyseerd.Catalogus

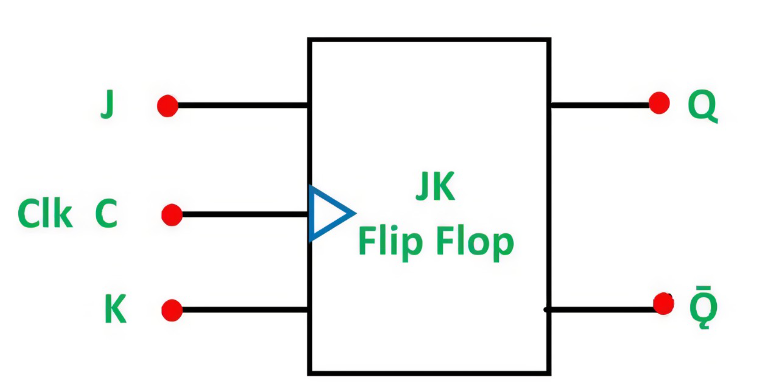

Figuur 1: JK Flip-Flop

Basics van JK Flip-Flop

De JK Flip-Flop is een basiscomponent in digitale elektronica, ontworpen om een beetje informatie op te slaan.Het bouwt voort op de eenvoudiger SR-flip-flop door feedback toe te voegen, wat helpt fouten te voorkomen die bekend staan als "rasomstandigheden", waarbij de output onstabiel wordt.

Deze flip-flop heeft twee hoofdingangen, j (set) en k (reset) en twee uitgangen: q en zijn complement, q '.Deze uitgangen weerspiegelen continu de huidige status en het tegenovergestelde, waardoor het circuit kan worden aangepast en reageert op realtime invoerwijzigingen.

De JK Flip-Flop werkt op specifieke manieren op basis van de invoerwaarden:

• Wanneer beide J en K 0 zijn: De flip-flop houdt zijn huidige status vast.Er komen geen veranderingen op.

• Wanneer beide J en K 1 zijn: De flip-flop schakelt zijn status op.Als Q 0 is, wordt het 1;Als Q 1 is, schakelt het over naar 0. Deze schakelactie is een sleutelfunctie die de JK Flip-Flop onderscheidt van eenvoudigere ontwerpen.

• Wanneer J 1 is en K 0 is: De flip-flop stelt zijn status in, waardoor Q gelijk is aan 1.

• Wanneer J 0 is en K 1 is: De flip-flop wordt gereset, waardoor Q gelijk is aan 0.

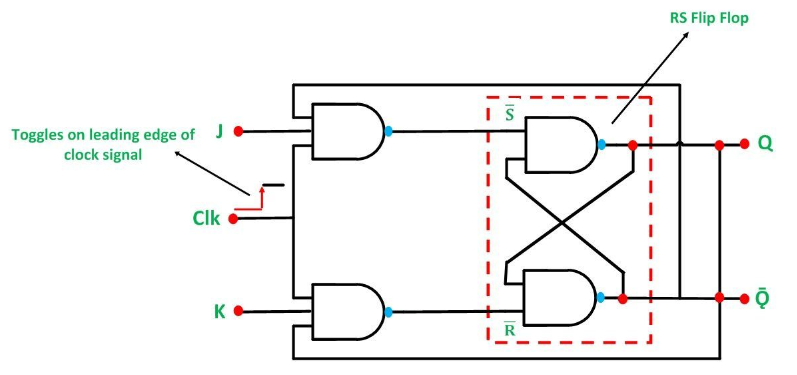

Werking van de JK Flip-flop

De JK Flip-Flop speelt een sleutelrol in digitale circuits door geheugen en timing te beheren via een gecoördineerde reactie op invoersignalen en klokpulsen.De werking ervan hangt sterk af van de timing van de J- en K -ingangen ten opzichte van het kloksignaal, dat bepaalt hoe de uitgangsstatus (Q en Q̅) veranderen.Deze synchronisatie zorgt ervoor dat de flip-flop zich voorspelbaar gedraagt in verschillende circuittoepassingen.De flip-flop vertrouwt op NAND of noch poorten om deze staatsveranderingen te beheren.

Houd de huidige status vast- Wanneer beide J- en K-ingangen laag zijn (0), houdt de flip-flop zijn huidige status.De logische poorten "vergrendelen" de uitgangen, waardoor de vorige toestand (hoog of laag) wordt gehandhaafd.Deze houdfunctie is ernstig in toepassingen waar gegevens stabiel moeten blijven totdat een specifieke wijziging een must is.

De uitgang HOOG instellen (Staat instellen) -Wanneer de klokpuls optreedt en J hoog is (1) terwijl K laag blijft (0), passen de logische poorten zich aan om de flip-flop in te stellen.Dit drijft de output Q naar een hoge toestand (1).Dit is handig in situaties waarin het circuit een hoge uitvoer moet activeren, bijvoorbeeld het activeren van een apparaat of het opslaan van een "1" in het geheugen.

De output laag wissen (reset -status) - Als J laag is (0) en K hoog is (1) op het moment van een klokpuls, gaat de flip-flop over in een resetstatus, waardoor Q wordt gedwongen laag te gaan (0).Deze resettende actie wordt vaak gebruikt in circuits die een standaard- of gewiste status nodig hebben na het voltooien van een bewerking, zoals het wissen van gegevens uit het geheugen.

De uitgang schakelen - De unieke functie van de flip-flop komt naar voren wanneer zowel J als K hoog zijn (1).Wanneer de klokpuls arriveert, schakelt de flip-flop schakelt en schakelt de uitgang van de huidige status naar de tegenovergestelde.Als Q hoog is, wordt het laag en als Q laag is, wordt het hoog.Deze schakelfunctie is aandringen in toepassingen zoals tellers of apparaten die automatisch tussen staten moeten afwisselen.

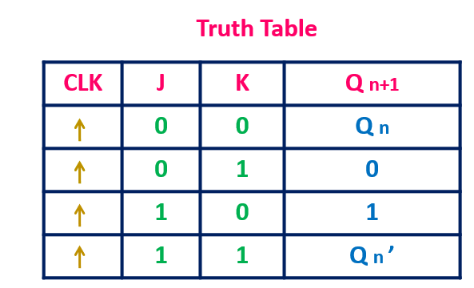

Figuur 2: JK Flip-Flop Truth Table

Jk flip-flop waarheidstabelanalyse

De waarheidstabel van de JK Flip-Flop is een belangrijk hulpmiddel om te visualiseren hoe deze reageert op verschillende invoersignalen synchroon met klokpulsen.Deze tabel helpt bij het ontwerpen van en het oplossen van digitale circuits door te laten zien hoe de uitvoer van de flip-flop veranderen op basis van verschillende invoeromstandigheden.

• Zowel J als K laag (J = 0, K = 0): Wanneer beide ingangen 0 zijn, houdt de flip-flop zijn huidige status vast.Of Q hoog of laag is, het blijft ongewijzigd.Dit is opmerkelijk voor circuits waar stabiele gegevensbehoud wordt gewenst, zoals elementen in het geheugen, waarbij het behoud van de huidige status geschikt is totdat een specifieke wijziging is geactiveerd.

• J hoog, k laag (j = 1, k = 0): Wanneer J 1 is en K 0 is, stelt de flip-flop de uitgang Q op hoog (1) in.Deze instellingsconditie is nuttig in toepassingen die een precieze trigger vereisen om een bewerking te activeren, zoals het inschakelen van een apparaat of het initiëren van een reeks in een logisch circuit.

• J laag, k high (j = 0, k = 1): Met J op 0 en K op 1, reset de flip-flop, waardoor q laag wordt (0).Deze reset -functie is ernstig in systemen die moeten terugkeren naar een standaardstatus, zoals bij het wissen van gegevens of het initialiseren van een proces.

• Zowel J als K High (J = 1, K = 1): Wanneer beide ingangen hoog zijn, schakelt de flip-flop zijn toestand.Als Q hoog is, wordt het laag en als Q laag is, schakelt het over naar hoog.Dit schakelgedrag is substantieel voor apparaten die moeten worden afgewisseld tussen staten, zoals in frequentiedelers of tellers.

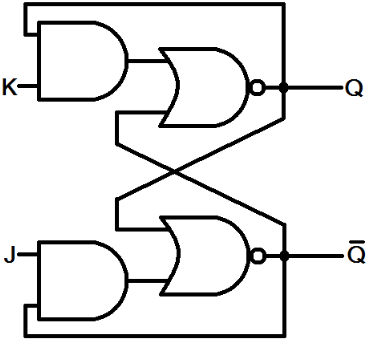

Figuur 3: JK Latch

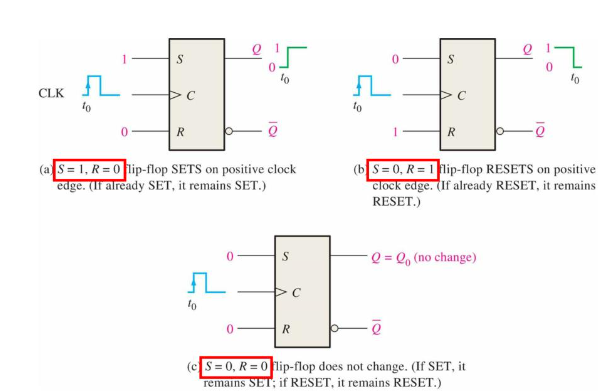

Inzichten in JK Latch -operatie en gebruik

De JK-vergrendeling werkt op dezelfde manier als de JK Flip-flop, maar zonder de noodzaak van een kloksignaal.In plaats van te wachten op een klokrand, reageert de JK-vergrendeling continu op het invoeren van wijzigingen, waardoor het "niveau-gevoelig" is.Dit betekent dat zolang de inputs (J en K) stabiel zijn, de output in realtime zal veranderen en onmiddellijke feedback biedt op basis van de invoervoorwaarden.

In tegenstelling tot de rand-triggered JK Flip-Flop, die de uitvoer alleen bijwerkt wanneer het kloksignaal verandert (van laag naar hoog of vice versa), past de JK-vergrendeling zijn uitgang onmiddellijk aan als ingangen verschuift.Deze constante, realtime responsiviteit is waardevol in scenario's waarbij onmiddellijke actie gewenst is zonder de vertraging veroorzaakt door kloksynchronisatie.

Ruisfilters: In digitale circuits die snel ongewenste ruis moeten filteren, is de onmiddellijke reactie van de JK -vergrendeling op inputveranderingen invloedrijk.Omdat het niet wacht op een klokpuls, kan het de uitgang aanpassen zodra ruis wordt gedetecteerd, waardoor vertragingen in signaalcorrectie worden voorkomen.

Eenvoudige geheugenelementen: De JK -vergrendeling kan dienen als een basisgeheugeneenheid in systemen die geen complexe, geklokte bediening vereisen.Omdat de vergrendeling de uitgang stabiel houdt zolang de ingangen niet veranderen, bevat het effectief de huidige status, wat nuttig is voor circuits die informatie moeten bewaren zonder de overhead van geklokte bewerkingen.

Figuur 4: Timing-diagramanalyse voor de JK Flip-Flop

Analyse van het timingdiagram van JK Flip-Flops

Een timingdiagram van de JK-flip-flop biedt een visuele uitsplitsing van hoe de uitgang reageert op verschillende ingangen, gesynchroniseerd met de pulsovergangen van de klok.Dit diagram toont de relatie tussen het kloksignaal (CLK) en de ingangen (J en K), en hoe ze gezamenlijk de uitgangen beïnvloeden (Q en Q ').Het helpt het gedrag van de flip-flop in kaart te brengen in sequentiële toestanden, waardoor het gemakkelijker is om de werking ervan te begrijpen.

Ten eerste, het diagram benadrukt dat de uitgangen alleen worden bijgewerkt op de stijgende of dalende randen van de klokpuls.Deze functie, bekend als rand-triggering, is dominant voor de werking van de JK Flip-flop.Het laat zien dat zelfs als de ingangen J en K veranderen, de uitgang ongewijzigd blijft totdat de klokrand optreedt, waardoor voorspelbare en stabiele overgangen worden gewaarborgd.

Terwijl het diagram dan de variaties van ingangen J en K toewijst, is het visueel toont aan hoe elke invoercombinatie de uitgang beïnvloedt. Wanneer beide J en K bijvoorbeeld laag zijn (0), bevat de uitgang zijn huidige status.Wanneer J hoog is en K laag is, is de uitgang ingesteld.Deze duidelijke visuele weergave helpt gebruikers te begrijpen hoe de flip-flop in realtime reageert op verschillende invoercombinaties.

Eindelijk, Het timingdiagram toont duidelijk de overgangen tussen verschillende uitgangsstatus, of het nu gaat om vasthouden, instellen, resetten of schakelen.Elke toestandsverandering is rechtstreeks gebonden aan de invoeromstandigheden en de klokrand, die een oorzaak-en-gevolg relatie toont die focaal is voor het ontwerpen en oplossen van problemen met problemen.

Veelzijdige toepassingen van JK flip-flops

JK flip-flops zijn kerncomponenten in een breed scala van digitale systemen, bekend om hun flexibiliteit en betrouwbaarheid.Hun vermogen om complexe logische bewerkingen af te handelen maakt ze vereist in verschillende belangrijke toepassingen, waaronder:

Figuur 5: Geheugenopslag

JK flip-flops worden vaak gebruikt om individuele stukjes gegevens op te slaan, waardoor ze fundamentele elementen in geheugenarrays en registers zijn.Elke flip-flop bevat een bit en zorgt voor betrouwbare gegevensopslag, die gunstig is in het ontwerp van grotere geheugensystemen.

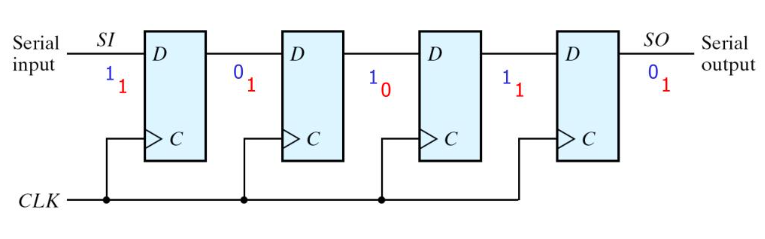

Figuur 6: Tellers en Shift Registers

JK flip-flops zijn dynamisch in sequencing-bewerkingen.Ze worden veel gebruikt in tellers voor het tellen van gebeurtenissen of pulsen en in shift -registers voor het omzetten van seriële gegevens in parallelle formaten.Dit maakt ze nuttig bij het beheren en manipuleren van gegevens in verschillende stadia van een proces, zoals in communicatiesystemen.

Figuur 7: Frequentiedeling

Bij signaalverwerking worden JK-flip-flops vaak gebruikt voor frequentiedeling.Door hun toestand te schakelen met elke klokpuls, verdelen ze de frequentie van het ingangssignaal, waardoor een langzamer, beter beheersbaar kloksignaal ontstaat.Dit is opmerkelijk in toepassingen zoals Clock Signal Management, waar de timingcontrole gewenst is.

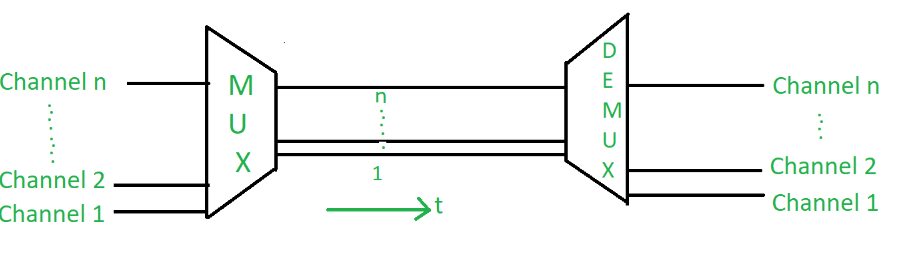

Figuur 8: Synchronisatie

JK flip-flops helpen bij het synchroniseren van meerdere digitale processen door ervoor te zorgen dat verschillende delen van een systeem op een gecoördineerde manier samenwerken.Ze zorgen ervoor dat verschillende componenten correct reageren op getimede signalen, waardoor het hele systeem synchroon blijft.

Figuur 9: JK Flip-Flop: rand-triggered en level-triggered

Verschillende soorten JK-flip-flops

JK flip-flops zijn verkrijgbaar in twee hoofdtypen: rand-triggered en level-triggered, elk ontworpen voor verschillende operationele vereisten.

Edge Triggered JK flip-flops: Verander hun toestand alleen op specifieke punten - wanneer de kloksignaalovergangen van laag naar hoog (stijgende rand) of hoog tot laag (dalende rand).Dit kenmerk maakt ze ideaal voor systemen waar precieze timing aandringen.Omdat toestandsveranderingen precies aan de rand van de klok optreden, zorgen deze flip-flops ervoor dat alle updates in synchronisatie plaatsvinden met de klokpuls.Dit voorspelbare gedrag is dynamisch in strak gecontroleerde omgevingen zoals digitale klokken, registers en de meeste opeenvolgende circuits.Hier is de timing van elke wijziging ernstig om de stabiliteit van het systeem te handhaven en ervoor te zorgen dat bewerkingen worden gesynchroniseerd.

Level-triggered JK flip-flops: anders werken, reageren op het ingangssignaal zolang het kloksignaal op een bepaald niveau is - hoog of laag.Ze wachten niet op een specifieke klokovergang.In plaats daarvan, zolang de input aan de vereiste voorwaarden voldoet, zal de flip-flop van staten veranderen.Dit gedrag maakt level-geactiveerde flip-flops beter geschikt voor asynchrone systemen, waarbij inputs mogelijk niet aansluiten bij een gewone klokpuls.Ze bieden flexibiliteit in systemen waarbij inputs onvoorspelbaar zijn of met onregelmatige intervallen aankomen, zoals in bepaalde signaalverwerkingstaken of monitoringsystemen die onmiddellijk moeten reageren op veranderende ingangen.

Voors en nadelen van jk flip-flop

JK Flip-Flops biedt verschillende voordelen, maar komen ook met enkele afwegingen die zorgvuldig moeten worden gewogen bij het ontwerpen van digitale systemen.

|

PROS |

|

|

Veelzijdigheid |

JK flip-flops zijn zeer flexibel en kan

worden gebruikt in verschillende digitale circuits zoals geheugenopslag, tellers en

Controlesystemen.Ze kunnen schakelen, instellen of resetten op basis van verschillende invoer

voorwaarden, waardoor ze geschikt zijn voor een breed scala aan toepassingen die

Nauwkeurige controle vereisen over overgangen van de toestand. |

|

Zelfcorrigerend mechanisme |

Een van de opvallende kenmerken van JK

Flip-flops is hun ingebouwde feedback-lus, die helpt logisch te corrigeren

Staat dynamisch.Deze zelfcorrectie zorgt ervoor dat het circuit blijft

Stabiel tijdens de werking, zelfs wanneer ingangen snel veranderen. |

|

Race Condition Mitigation |

In tegenstelling tot eenvoudiger flip-flops, JK flip-flops

zijn ontworpen om raceomstandigheden te voorkomen - beveiligingen waar de output wordt

Onstabiel vanwege conflicterende invoersignalen.Dit vermogen om te onderhouden

consistente uitvoer, zelfs onder snelle en sequentiële inputveranderingen, verbetert de

Betrouwbaarheid van het circuit. |

|

Nadelen |

|

|

Complex ontwerp |

JK flip-flops zijn ingewikkelder dan

Basis flip-flops.Hun ontwerp vereist extra logische poorten en input

monitoring, waardoor het circuit moeilijker te ontwerpen is en

Problemen oplossen, vooral in systemen waar eenvoud de voorkeur heeft. |

|

Voortplantingsvertraging |

De interne poort die wordt gebruikt om de staat te beheren

Overgangen introduceren een vertraging in hoe snel signalen kunnen worden verwerkt.In

High-speed-toepassingen, deze vertraging kan de totale timing beïnvloeden en vertragen

de prestaties van het circuit. |

|

Hoger stroomverbruik |

Vanwege hun complexiteit en de noodzaak om

Controleer voortdurend invoervoorwaarden, JK flip-flops verbruiken meer kracht

vergeleken met eenvoudiger flip-flops.In grotere systemen of vermogensgevoelig

Toepassingen, deze hogere stroomvraag kan een nadeel worden |

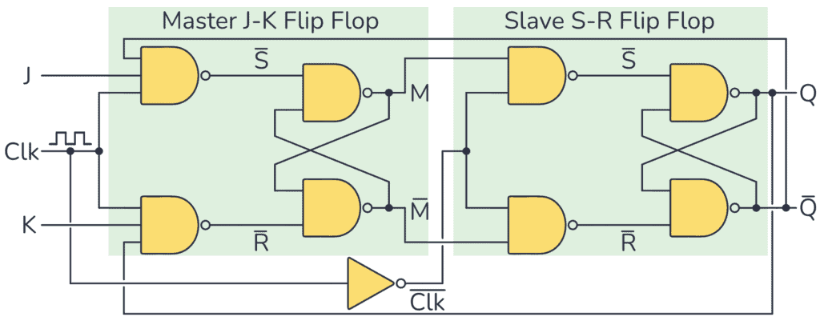

Figuur 10: Master-slave JK Flip-Flop

Het decoderen van de master-slave JK flip-flop

De Master-Slave JK Flip-Flop is ontworpen om de race-around toestand op te lossen die wordt gevonden in standaard JK-flip-flops met behulp van een tweestapsproces om ingangen en uitgangen efficiënter te beheren.

De eerste fase, de hoofdfase genoemd, legt de invoerwaarden vast wanneer het kloksignaal een specifieke rand bereikt, ofwel stijgt of valt.Op dit punt worden de invoergegevens vergrendeld, wat betekent dat verder wijzigingen in de ingangen de vastgelegde status niet tot de volgende klokcyclus beïnvloeden.Deze fase zorgt ervoor dat de flip-flop de juiste invoer registreert zonder te worden beïnvloed door latere wijzigingen tijdens dezelfde klokcyclus.

Nadat de hoofdfase is voltooid, speelt de slavenfase in het spel.Deze fase werkt de uitvoer bij op basis van de gegevens die zijn vastgelegd door de hoofdfase, maar alleen bij de volgende klokrand.Door de invoeropvang van de uitvoerupdate te scheiden, zorgt de slavenfase ervoor dat de uitgang stabiel blijft totdat de masterfase de invoer volledig heeft verwerkt.Dit voorkomt voortijdige of onbedoelde veranderingen in de uitgang tijdens de klokcyclus.

Waarom de configuratie van de master-slave is belangrijk?

Het tweetrapsproces stabiliseert de werking van de JK flip-flop, waardoor ongewenste oscillaties of schommelingen kunnen gebeuren die kunnen plaatsvinden in eenvoudigere configuraties, vooral wanneer beide ingangen hoog worden gehouden.Door de invoerverwerking van de uitvoerwijziging te ontkoppelen, zorgt de hoofdslave-configuratie ervoor dat uitgangen voorspelbaar en stabiel blijven, zelfs in situaties waarin timing waardevol is.

De race rond de staat aanspreken in JK Flip-Flops

Race-around omstandigheden komen voor in JK-flip-flops wanneer beide ingangen, J en K, hoog zijn en het kloksignaal blijft te lang actief.Dit leidt tot continu schakelen van de uitgangen, wat onregelmatig gedrag kan veroorzaken en de betrouwbaarheid van het circuit kan verstoren.

De master-slave-opstelling maakt gebruik van een tweetrapsproces om race-around problemen te voorkomen.De hoofdfase vangt de invoerwaarden aan de klokrand en vergrendelt ze. De slavenfase werkt de uitgangen bij de volgende klokrand bij, zodat de uitgang niet verandert totdat de ingangen volledig zijn verwerkt.Deze benadering voorkomt effectief dat de uitgang oncontroleerbaar schakelt, zelfs als de ingangen gedurende een langere periode hoog blijven.

Een andere methode om race-around omstandigheden te voorkomen, is het aanpassen van de klokpulsduur.Door de klokpuls korter te maken dan de voortplantingsvertraging van de flip-flop, kunt u ervoor zorgen dat de status niet meer dan eens verandert binnen dezelfde klokcyclus.Dit voorkomt dat de flip-flop herhaaldelijk schakelt tijdens een enkele cyclus, waardoor de uitgang stabiliseert.

Dynamiek van schakelen in JK-flip-flops

Het schakelgedrag van een JK-flip-flop wordt grotendeels aangedreven door de timing van het kloksignaal en de ingangsniveaus (J en K).De flip-flop verandert van status op basis van de ingangen die aanwezig zijn aan de positieve rand van het kloksignaal.Op dit gevaarlijke moment evalueert de flip-flop de inputs en werkt de uitvoer ervan dienovereenkomstig bij.

Wanneer het kloksignaal de stijgende rand raakt, leest de JK flip-flop de huidige toestanden van de J- en K-ingangen.Afhankelijk van hun waarden zal de flip-flop de uitvoer vasthouden, instellen, resetten of schakelen.

Digitale klokken: Nauwkeurigheid is alles in digitale klokken, en JK flip-flops helpen deze precisie te behouden door ervoor te zorgen dat statuswijzigingen alleen plaatsvinden met precieze klokintervallen.

Sequentiële logische testers: In systemen die de functionaliteit van logische circuits testen, spelen JK flip-flops een rol bij het verifiëren dat elke component correct reageert op specifieke getimede signalen.

Andere tijdgevoelige systemen: In verschillende digitale toepassingen waar timing riskant is, zoals communicatiesystemen of gegevensverwerkingseenheden, zorgt de JK FLIP-flop ervoor dat statusovergangen in synchronisatie met de klok plaatsvinden, waardoor timingfouten voorkomen.

Conclusie

De JK Flip-Flop valt op als een ultiem element in het ontwerp van het digitale circuit en biedt een mix van veelzijdigheid en precisie wanhopig op zoek naar een breed scala aan toepassingen, variërend van geheugenopslag tot frequentiedivisie en synchronisatie van digitale processen.Het vermogen om raceomstandigheden te verminderen door innovatieve configuraties zoals de master-slave-opstelling onderstreept zijn aanpassingsvermogen bij het oplossen van inherente ontwerpuitdagingen.Evenzo benadrukt de ernstige rol van de flip-flop bij het waarborgen van precieze overgangen van de toestand ervan de vereiste aard van het creëren en onderhoud van betrouwbare en efficiënte digitale systemen.Naarmate de technologie vordert, blijven de evoluerende ontwerpen en toepassingen van de JK Flip-flop de sleutel tot het verleggen van de grenzen van digitale elektronica naar meer geavanceerde en robuuste architecturen.

Veelgestelde vragen [FAQ]

1. Wat zijn de toepassingen van JK Flip Flop?

De JK Flip-Flop wordt veelvuldig gebruikt in digitale elektronica voor verschillende taken:

Timingtoepassingen: Het kan dienen als een vertragingselement of een timer wanneer het in bepaalde configuraties is aangesloten.

Tellers en registers: Door zijn toestand te schakelen met elke klokpuls, wordt deze gebruikt bij het ontwerpen van verschillende tellers en schakelregisters die ultiem zijn in sequentiële logische circuits.

Geheugenopslag: Het biedt een basiseenheid van geheugenopslag, nuttig bij het opslaan van bits in computationele toepassingen.

2. Hoe werkt een JK flip-flop met een waarheidstabel?

Een JK Flip-Flop heeft twee ingangen (J en K) en een kloksignaal.De werking ervan varieert op basis van de invoertoestanden, gesynchroniseerd met de klok:

• j = 0, k = 0: de uitvoer verandert niet.

• j = 0, k = 1: de uitgang wordt gereset op 0.

• j = 1, k = 0: de uitvoer is ingesteld op 1.

• j = 1, k = 1: de uitgang schakelt (d.w.z. als het 0 was, wordt het 1 en vice versa).

3. Wat is JK Flip Flop en werkt het?

Een JK Flip-Flop combineert de eigenschappen van SR- en T-flip-flops.Het vermijdt de "verboden" toestand die wordt gezien in SR-flip-flops door de JK-ingangen effectief te gebruiken:

De toestand van de flip-flop wordt geregeld door de ingangen J en K, die bepalen of de uitgang moet vasthouden, resetten, ingesteld of schakelen, synchroon met de stijgende of dalende rand van de klokpuls.

4. Wat zijn de toepassingen van vergrendelingen en slippers?

Gegevensopslag: Vergrendeling en flip-flops zijn serieus voor gegevensopslag binnen registers en geheugenarrays.

Frequentiedivisie: Gebruikt in frequentiedividers vanwege hun vermogen om van staten aan de klokranden te veranderen, waardoor de frequentie met elke fase in een serie wordt gehalveerd.

Staatsmachines: Basis bij het ontwerpen van eindige statusmachines die worden gebruikt om sequentiële logica en besturingscircuits te implementeren.

Ontdaken: Gebruikt om signalen van mechanische schakelaars en knoppen te stabiliseren, waardoor enkele, schone overgangen worden gewaarborgd.

5. Waar worden flip-flops gebruikt?

Binaire opslag: Elke flip-flop slaat een beetje gegevens op, waardoor ze bouwstenen voor binaire opslagapparaten zijn.

Klokverdeling: Ze verdelen de invoerklokfrequentie door twee, nuttig in digitale klokken en timingtoepassingen.